# **Feature Summary**

- 32-bit load/store AVR32B RISC architecture

- 15 general-purpose 32-bit registers

- 32-bit Stack Pointer, Program Counter and Link Register reside in register file

- Fully orthogonal instruction set

- Pipelined architecture allows one instruction per clock cycle for most instructions

- Byte, half-word, word and double word memory access

- Shadowed interrupt context for INT3 and multiple interrupt priority levels

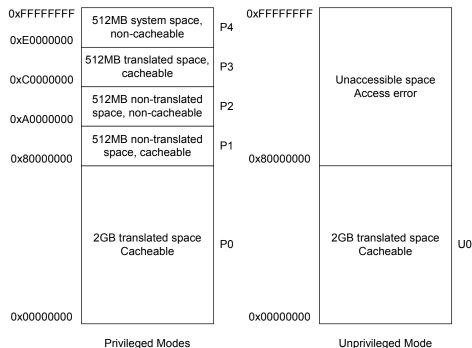

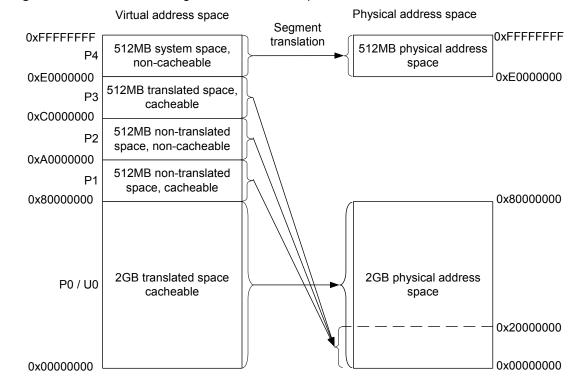

- Privileged and unprivileged modes enabling efficient and secure Operating Systems

- Full MMU allows for operating systems with memory protection

- Instruction and data caches

- Innovative instruction set together with variable instruction length ensuring industry leading code density

- DSP extention with saturating arithmetic, and a wide variety of multiply instructions

- SIMD extention for media applications

- Dynamic branch prediction and return address stack for fast change-of-flow

- Powerful On-Chip Debug system

- Coprocessor interface

32-bit AVR<sup>®</sup> Microcontroller

AVR32 AP Technical Reference Manual

32001A-AVR32-06/06

# 1. Introduction

AVR<sup>®</sup>32 is a new high-performance 32-bit RISC microprocessor core, designed for cost-sensitive embedded applications, with particular emphasis on low power consumption and high code density. In addition, the instruction set architecture has been tuned to allow for a variety of microarchitectures, enabling the AVR32 to be implemented as low-, mid- or high-performance processors.

# 1.1 The AVR family

The AVR family was launched by Atmel<sup>®</sup> in 1996 and has had remarkable success in the 8-and 16-bit flash microcontroller market. AVR32 complements the current AVR microcontrollers. Through the AVR32 family, the AVR is extended into a new range of higher performance applications that is currently served by 32- and 64-bit processors

To truly exploit the power of a 32-bit architecture, the new AVR32 architecture is not binary compatible with earlier AVR architectures. In order to achieve high code density, the instruction format is flexible providing both compact instructions with 16 bits length and extended 32-bit instructions. While the instruction length is only 16 bits for most instructions, powerful 32-bit instructions are implemented to further increase performance. Compact and extended instructions can be freely mixed in the instruction stream.

# 1.2 The AVR32 Microprocessor Architecture

The AVR32 is a new innovative microprocessor architecture. It is a fully synchronous synthesisable RTL design with industry standard interfaces, ensuring easy integration into SoC designs with legacy intellectual property (IP). Through a quantitative approach, a large set of industry recognized benchmarks have been compiled and analyzed to achieve the best code density in its class of microprocessor architectures. In addition to lowering the memory requirements, a compact code size also contributes to the core's low power characteristics. The processor supports byte and half-word data types without penalty in code size and performance.

Memory load and store operations are provided for byte, half-word, word and double word data with automatic sign- or zero extension of half-word and byte data. The C-compiler is closely linked to the architecture and is able to exploit code optimization features, both for size and speed.

In order to reduce code size to a minimum, some instructions have multiple addressing modes. As an example, instructions with immediates often have a compact format with a smaller immediate, and an extended format with a larger immediate. In this way, the compiler is able to use the format giving the smallest code size.

Another feature of the instruction set is that frequently used instructions, like add, have a compact format with two operands as well as an extended format with three operands. The larger format increases performance, allowing an addition and a data move in the same instruction in a single cycle.

Load and store instructions have several different formats in order to reduce code size and speed up execution:

- · Load/store to an address specified by a pointer register

- · Load/store to an address specified by a pointer register with postincrement

- Load/store to an address specified by a pointer register with predecrement

- Load/store to an address specified by a pointer register with displacement

- Load/store to an address specified by a small immediate (direct addressing within a small page)

- Load/store to an address specified by a pointer register and an index register.

The register file is organized as 16 32-bit registers and includes the Program Counter, the Link Register, and the Stack Pointer. In addition, one register is designed to hold return values from function calls and is used implicitly by some instructions.

The AVR32 architecture defines several microarchitectures in order to capture the entire range of applications. The microarchitectures are named AVR32A, AVR32B and so on. Different microarchitectures are suited to different end applications, allowing the designer to select a microarchitecture with the optimum set of parameters for a specific application.

# 1.3 Event handling

The AVR32 incorporates a powerful event handling scheme. The different event sources, like "Illegal opcode" and external interrupt requests, have different priority levels, ensuring a welldefined behavior when multiple events are received simultaneously. Additionally, pending events of a higher priority class may preempt handling of ongoing events of a lower priority class. Each priority class has dedicated registers to keep the return address and status register thereby removing the need to perform time-consuming memory operations to save this information.

There are four levels of external interrupt requests, all executing in their own context. An interrupt controller does the priority handling of the external interrupts and provides the prioritized interrupt vector to the processor core.

# 1.4 Java Support

The AVR32 architecture defines a Java<sup>®</sup> hardware acceleration option, in the form of a Java Virtual Machine hardware implementation.

# 1.5 Microarchitectures

The AVR32 architecture defines different microarchitectures. This enables implementations that are tailored to specific needs and applications. The microarchitectures provide different performance levels at the expense of area and power consumption. The following microarchitectures are defined:

#### 1.5.1 AVR32A

The AVR32A microarchitecture is targeted at cost-sensitive, lower-end applications like smaller microcontrollers. This microarchitecture does not provide dedicated hardware registers for shadowing of register file registers in interrupt contexts. Additionally, it does not provide hardware registers for the return address registers and return status registers. Instead, all this information is stored on the system stack. This saves chip area at the expense of slower interrupt handling.

Upon interrupt initiation, registers R8-R12 are automatically pushed to the system stack. These registers are pushed regardless of the priority level of the pending interrupt. The return address and status register are also automatically pushed to stack. The interrupt handler can therefore use R8-R12 freely. Upon interrupt completion, the old R8-R12 registers and status register are restored, and execution continues at the return address stored popped from stack.

The stack is also used to store the status register and return address for exceptions and *scall*. Executing the *rete* or *rets* instruction at the completion of an exception or system call will pop this status register and continue execution at the popped return address.

## 1.5.2 AVR32B

The AVR32B microarchitecture is targeted at applications where interrupt latency is important. The AVR32B therefore implements dedicated registers to hold the status register and return address for interrupts, exceptions and supervisor calls. This information does not need to be written to the stack, and latency is therefore reduced. Additionally, AVR32B allows hardware shadowing of the registers in the register file. The INT0 to INT3 contexts may have dedicated versions of the registers in the register file, allowing the interrupt routine to start executing immediately.

The *scall, rete* and *rets* instructions use the dedicated status register and return address registers in their operation. No stack accesses are performed.

**AVR32**

# 1.6 The AVR32 AP implementation

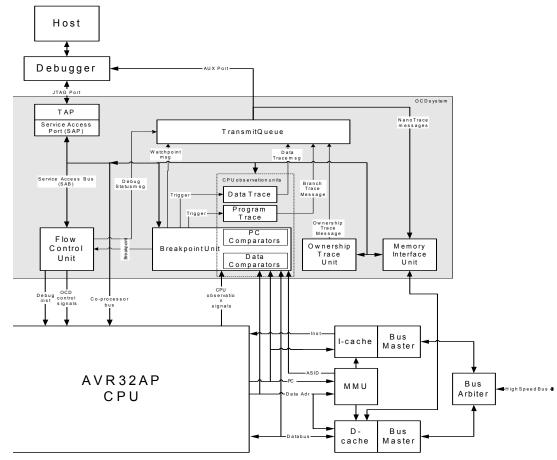

The first implementation of the AVR32B microarchitecture is designed as an application processor and called AVR32 AP. This implementation targets high-performance applications in the DSP, multimedia and wireless segment, and provides:

- Advanced OCD system.

- Efficient data and instruction caches.

- Full MMU.

- Java acceleration is implemented in hardware.

- Fast interrupt handling is provided through shadowed register banks for interrupt priority 3.

- SIMD extension.

- DSP extension.

- Service Access Port (SAP) that gives an external JTAG controller access to memories and registers inside the AVR32 AP core.

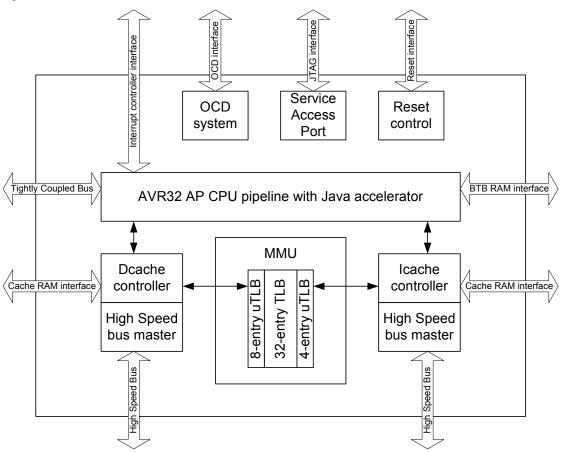

Figure 1-1 on page 5 displays the contents of AVR32 AP:

Figure 1-1. Overview of AVR32 AP.

# 2. Programming Model

This chapter describes the programming model and the set of registers accessible to the user. It also describes the implementation options in AVR32 AP.

# 2.1 Architectural compatibility

AVR32 AP is fully compatible with the Atmel AVR32B architecture.

# 2.2 Implementation options

## 2.2.1 Memory management

AVR32 AP implements a full MMU as specified by the AVR32 architecture.

# 2.2.2 Java support

AVR32 AP implements a Java Extention Module (JEM) as defined in the AVR32 architecture.

# 2.3 Register file configuration

The AVR32B architecture specifies that the exception contexts may have a different number of shadowed registers in different implementations. The following shadow model is used in AVR32 AP.

| Application  | Supervisor   | INT0         | INT1         | INT2         | INT3         | Exception    | NMI          |

|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Bit 31 Bit 0 |

| PC           |

| LR           | LR           | LR           | LR           | LR           | LR_INT3      | LR           | LR           |

| SP_APP       | SP_SYS       |

| R12          | R12          | R12          | R12          | R12          | R12_INT3     | R12          | R12          |

| R11          | R11          | R11          | R11          | R11          | R11_INT3     | R11          | R11          |

| R10          | R10          | R10          | R10          | R10          | R10_INT3     | R10          | R10          |

| R9           | R9           | R9           | R9           | R9           | R9_INT3      | R9           | R9           |

| R8           | R8           | R8           | R8           | R8           | R8_INT3      | R8           | R8           |

| R7           |

| R6           |

| R5           |

| R4           |

| R3           |

| R2           |

| R1           |

| R0           |

| SR           |

|              | RSR_SUP      | RSR_INT0     | RSR_INT1     | RSR_INT2     | RSR_INT3     | RSR_EX       | RSR_NMI      |

|              | RAR_SUP      | RAR_INT0     | RAR_INT1     | RAR_INT2     | RAR_INT3     | RAR_EX       | RAR_NMI      |

Figure 2-1. Register file configuration. Shadowed registers are marked in grey.

# 2.4 Status register configuration

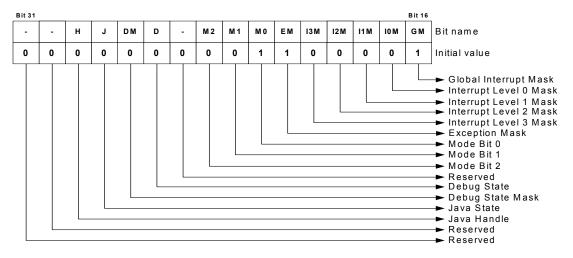

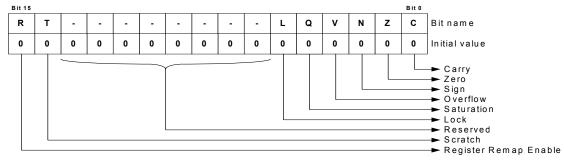

The Status Register (SR) is splitted into two halfwords, one upper and one lower. The lower word contains the C, Z, N, V and Q condition code flags and the R, T and L bits, while the upper halfword contains information about the mode and state the processor executes in.

Figure 2-2. The Status Register high halfword.

Figure 2-3. The Status Register low halfword.

# H - Java Handle

This bit is included to support different heap types in the Java Virtual Machine. For more details, see the Java Technical Reference manual. The bit is cleared at reset.

# J - Java state

The processor is in Java state when this bit is set. The incoming instruction stream will be decoded as a stream of Java bytecodes, not RISC opcodes. The bit is cleared at reset. This bit should not be modified by the user as undefined behaviour may result.

# DM - Debug State Mask

If this bit is set, the Debug State is masked and cannot be entered. The bit is cleared at reset, and can both be read and written by software.

# D - Debug state

The processor is in debug state when this bit is set. The bit is cleared at reset and should only be modified by debug hardware, the *breakpoint* instruction or the *retd* instruction. Undefined behaviour may result if the user tries to modify this bit manually.

## M2, M1, M0 - Execution Mode

These bits show the active execution mode. The different settings for the different modes are shown in Table 2-1. M2 and M1 are cleared by reset while M0 is set so that the processor is in supervisor mode after reset. These bits are modified by hardware, or execution of certain instructions like *scall*, *rets* and *rete*. Undefined behaviour may result if the user tries to modify these bits manually.

| M2 | M1 | МО | Mode                   |

|----|----|----|------------------------|

| 1  | 1  | 1  | Non Maskable Interrupt |

| 1  | 1  | 0  | Exception              |

| 1  | 0  | 1  | Interrupt level 3      |

| 1  | 0  | 0  | Interrupt level 2      |

| 0  | 1  | 1  | Interrupt level 1      |

| 0  | 1  | 0  | Interrupt level 0      |

| 0  | 0  | 1  | Supervisor             |

| 0  | 0  | 0  | Application            |

Table 2-1. Mode bit settings

# EM - Exception mask

When this bit is set, exceptions are masked. Exceptions are enabled otherwise. The bit is automatically set when exception processing is initiated or Debug Mode is entered. Software may clear this bit after performing the necessary measures if nested exceptions should be supported. This bit is set at reset.

#### I3M - Interrupt level 3 mask

When this bit is set, level 3 interrupts are masked. If I3M and GM are cleared, INT3 interrupts are enabled. The bit is automatically set when INT3 processing is initiated. Software may clear this bit after performing the necessary measures if nested INT3s should be supported. This bit is cleared at reset.

#### I2M - Interrupt level 2 mask

When this bit is set, level 2 interrupts are masked. If I2M and GM are cleared, INT2 interrupts are enabled. The bit is automatically set when INT3 or INT2 processing is initiated. Software may clear this bit after performing the necessary measures if nested INT2s should be supported. This bit is cleared at reset.

#### I1M - Interrupt level 1 mask

When this bit is set, level 1 interrupts are masked. If I1M and GM are cleared, INT1 interrupts are enabled. The bit is automatically set when INT3, INT2 or INT1 processing is initiated. Software may clear this bit after performing the necessary measures if nested INT1s should be supported. This bit is cleared at reset.

**AVR32**

#### IOM - Interrupt level 0 mask

When this bit is set, level 0 interrupts are masked. If IOM and GM are cleared, INT0 interrupts are enabled. The bit is automatically set when INT3, INT2, INT1 or INT0 processing is initiated. Software may clear this bit after performing the necessary measures if nested INT0s should be supported. This bit is cleared at reset.

#### **GM - Global Interrupt Mask**

When this bit is set, all interrupts are disabled. This bit overrides I0M, I1M, I2M and I3M. The bit is automatically set when exception processing is initiated, Debug Mode is entered, or a Java trap is taken. This bit is automatically cleared when returning from a Java trap. This bit is set after reset.

## R - Java Register Remap

When this bit is set, the addresses of the registers in the register file is dynamically changed. This allows efficient use of the register file registers as a stack. For more details, see the Java Technical Reference Manual. The R bit is cleared at reset. Undefined behaviour may result if this bit is modified by the user.

## T - Scratch bit

Not used by any instruction, but can be manipulated by application software as a scratchpad bit. This bit is cleared after reset.

## L - Lock flag

Used by the conditional store instruction. Used to support atomical memory access. Automatically cleared by *rete*. This bit is cleared after reset.

#### Q - Saturation flag

The saturation flag indicates that a saturating arithmetic operation overflowed. The flag is sticky and once set it has to be manually cleared by a *csrf* instruction after the desired action has been taken. See the Instruction set description for details.

#### V - Overflow flag

The overflow flag indicates that an arithmetic operation overflowed. See the Instruction set description for details.

#### N - Negative flag

The negative flag is modified by arithmetical and logical operations. See the Instruction set description for details.

#### Z - Zero flag

The zero flag indicates a zero result after an arithmetic or logic operation. See the Instruction set description for details.

#### C - Carry flag

The carry flag indicates a carry after an arithmetic or logic operation. See the Instruction set description for details.

# 2.5 System registers

The system registers are placed outside of the virtual memory space, and are only accessible using the privileged *mfsr* and *mtsr* instructions. Some of the System Registers can be altered automatically by hardware. The table below lists the system registers specified in AVR32 AP. It also identifies their address and the pipeline stage in which it is located. The programmer is responsible for maintaining correct sequencing of any instructions following a *mtsr* instruction.

| Reg # | Address | Name     | Function                                       | Location<br>in pipeline |

|-------|---------|----------|------------------------------------------------|-------------------------|

| 0     | 0       | SR       | Status Register                                | A1                      |

| 1     | 4       | EVBA     | Exception Vector Base Address                  | A1                      |

| 2     | 8       | ACBA     | Application Call Base Address                  | A1                      |

| 3     | 12      | CPUCR    | CPU Control Register                           | A1                      |

| 4     | 16      | ECR      | Exception Cause Register                       | A1                      |

| 5     | 20      | RSR_SUP  | Return Status Register for supervisor context  | A1                      |

| 6     | 24      | RSR_INT0 | Return Status Register for INT 0 context       | A1                      |

| 7     | 28      | RSR_INT1 | Return Status Register for INT 1 context       | A1                      |

| 8     | 32      | RSR_INT2 | Return Status Register for INT 2 context       | A1                      |

| 9     | 36      | RSR_INT3 | Return Status Register for INT 3 context       | A1                      |

| 10    | 40      | RSR_EX   | Return Status Register for Exception context   | A1                      |

| 11    | 44      | RSR_NMI  | Return Status Register for NMI context         | A1                      |

| 12    | 48      | RSR_DBG  | Return Status Register for Debug Mode          | A1                      |

| 13    | 52      | RAR_SUP  | Return Address Register for supervisor context | A1                      |

| 14    | 56      | RAR_INT0 | Return Address Register for INT 0 context      | A1                      |

| 15    | 60      | RAR_INT1 | Return Address Register for INT 1 context      | A1                      |

| 16    | 64      | RAR_INT2 | Return Address Register for INT 2 context      | A1                      |

| 17    | 68      | RAR_INT3 | Return Address Register for INT 3 context      | A1                      |

| 18    | 72      | RAR_EX   | Return Address Register for Exception context  | A1                      |

| 19    | 76      | RAR_NMI  | Return Address Register for NMI context        | A1                      |

| 20    | 80      | RAR_DBG  | Return Address Register for Debug Mode         | A1                      |

| 21    | 84      | JECR     | Java Exception Cause Register                  | A1                      |

| 22    | 88      | JOSP     | Java Operand Stack Pointer                     | ID                      |

| 23    | 92      | JAVA_LV0 | Java Local Variable 0                          | A1                      |

| 24    | 96      | JAVA_LV1 | Java Local Variable 1                          | A1                      |

| 25    | 100     | JAVA_LV2 | Java Local Variable 2                          | A1                      |

| 26    | 104     | JAVA_LV3 | Java Local Variable 3                          | A1                      |

| 27    | 108     | JAVA_LV4 | Java Local Variable 4                          | A1                      |

| 28    | 112     | JAVA_LV5 | Java Local Variable 5                          | A1                      |

Table 2-2. System Registers implemented in AVR32 AP

10 **AVR32**

| Reg # | Address | Name     | Function                             | Location<br>in pipeline |

|-------|---------|----------|--------------------------------------|-------------------------|

| 29    | 116     | JAVA_LV6 | Java Local Variable 6                | A1                      |

| 30    | 120     | JAVA_LV7 | Java Local Variable 7                | A1                      |

| 31    | 124     | JTBA     | Java Trap Base Address               | A1                      |

| 32    | 128     | JBCR     | Java Write Barrier Control Register  | A1                      |

| 64    | 256     | CONFIG0  | Configuration register 0             | тсв                     |

| 65    | 260     | CONFIG1  | Configuration register 1             | тсв                     |

| 66    | 264     | COUNT    | Cycle Counter register               | тсв                     |

| 67    | 268     | COMPARE  | Compare register                     | ТСВ                     |

| 68    | 272     | TLBEHI   | TLB Entry High                       | ТСВ                     |

| 69    | 276     | TLBELO   | TLB Entry Low                        | тсв                     |

| 70    | 280     | PTBR     | Page Table Base Register             | ТСВ                     |

| 71    | 284     | TLBEAR   | TLB Exception Address Register       | тсв                     |

| 72    | 288     | MMUCR    | MMU Control Register                 | тсв                     |

| 73    | 292     | TLBARLO  | TLB Accessed Register Low            | ТСВ                     |

| 74    | 296     | TLBARHI  | TLB Accessed Register High           | тсв                     |

| 75    | 300     | PCCNT    | Performance Clock Counter            | ТСВ                     |

| 76    | 304     | PCNT0    | Performance Counter 0                | тсв                     |

| 77    | 308     | PCNT1    | Performance Counter 1                | ТСВ                     |

| 78    | 312     | PCCR     | Performance Counter Control Register | ТСВ                     |

| 79    | 316     | BEAR     | Bus Error Address Register           | тсв                     |

| 192   | 768     | SABAL    | SAB Address Low Register             | тсв                     |

| 193   | 772     | SABAH    | SAB Address High Register            | тсв                     |

| 194   | 776     | SABD     | SAB Data Register                    | ТСВ                     |

| Table 2-2. | System Registers implemented in AVR32 AP | (Continued) |

|------------|------------------------------------------|-------------|

|            |                                          |             |

#### **SR - Status Register**

The Status Register is mapped into the system register space. This allows it to be loaded into the register file to be modified, or to be stored to memory. The Status Register is described in detail in Section 2.4 on page 7.

# **EVBA - Exception Vector Base Address**

This register contains a pointer to the exception routines. All exception routines starts at this address, or at a defined offset relative to the address. Special alignment requirements apply for EVBA, see Section 3.10 "Event handling" on page 30.

# **ACBA - Application Call Base Address**

Pointer to the start of a table of function pointers. Subroutines residing in this space can be called by the compact *acall* instruction. This facilitates efficient reuse of code. Keeping this base pointer as a register facilitates multiple application spaces. ACBA is a full 32 bit register, but the

lowest bit should be written to zero, making ACBA halfword aligned. Failing to do so may result in erroneous behaviour.

# **CPUCR - CPU Control Register**

Register controlling the configuration and behaviour of the CPU. The following fields are defined:

| Bit        | Name                  | Reset | Access             | Description                                                                                                                                                                                                                                                                                                                                                                           |

|------------|-----------------------|-------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 -<br>24 | COP7EN<br>-<br>COP0EN | 0     | Read/write         | Enable bit for coprocessor 7 to coprocessor 0. The<br>corresponding coprocessor is enabled if this bit is written<br>to one by software. Can be written to one only if the<br>corresponding coprocessor is present in the system.<br>Attempting to issue a coprocessor instruction to a<br>coprocessor whose enable bit is cleared, will result in a<br>coprocessor absent exception. |

| 5          | IEE                   | 1     | Read/write         | Imprecise Execution Enable. Required for various OCD features, see Section 9. "OCD system" on page 86. If cleared, memory operations will require several additional clock cycles.                                                                                                                                                                                                    |

| 4          | IBE                   | 1     | Read/write         | Imprecise Breakpoint Enable. Required for various OCD features, see Section 9. "OCD system" on page 86. If cleared, memory operations will require an additional clock cycle.                                                                                                                                                                                                         |

| 3          | RE                    | 1     | Read/write         | If set, the return stack is enabled. Disabling the return stack will empty it, removing all entries.                                                                                                                                                                                                                                                                                  |

| 2          | FE                    | 1     | Read/write         | If set, branch instructions can be folded with other instructions.                                                                                                                                                                                                                                                                                                                    |

| 1          | BE                    | 1     | Read/write         | If set, branch prediction is enabled.                                                                                                                                                                                                                                                                                                                                                 |

| 0          | BI                    | -     | Read-<br>0/write-1 | BTB invalidate. Writing to 1 will invalidate all entries in the BTB.                                                                                                                                                                                                                                                                                                                  |

| Other      | -                     | -     | Read-<br>0/write-0 | Unused. Read as 0. Should be written as 0.                                                                                                                                                                                                                                                                                                                                            |

**Table 2-3.**CPU control register

# **ECR - Exception Cause Register**

This register identifies the cause of the most recently executed exception. This information may be used to handle exceptions more efficiently in certain operating systems. The register is updated with a value equal to the EVBA offset of the exception, shifted 2 bit positions to the right. Only the 9 lowest bits of the EVBA offset are considered. As an example, an ITLB miss jumps to EVBA+0x50. The ECR will then be loaded with 0x50>2 == 0x14. The ECR register is not loaded when a Breakpoint or OCD Stop CPU exception is taken. Note that for interrupts, the offset is given by the autovector provided by the interrupt controller. The resulting ECR value may therefore overlap with an ECR value used by a regular exception. This can be avoided by choosing the autovector offsets so that no such overlaps occur.

# RSR\_SUP, RSR\_INT0, RSR\_INT1, RSR\_INT2, RSR\_INT3, RSR\_EX, RSR\_NMI - Return Status Registers

If a request for a mode change like an interrupt request is accepted when executing in a context C, the Status Register values in context C are automatically stored in the Return Status Register (RSR) associated with the interrupt context I. When the execution in the interrupt state I is fin-

**AVR32**

ished and the *rets / rete* instruction is encountered, the RSR associated with *I* is copied to SR, and the execution continues in the original context *C*.

#### RSR\_DBG - Return Status Register for Debug Mode

When Debug mode is entered, the status register contents of the original mode is automatically saved in this register. When the debug routine is finished, the *retd* instruction copies the contents of RSR\_DBG into SR.

# RAR\_SUP, RAR\_INT0, RAR\_INT1, RAR\_INT2, RAR\_INT3, RAR\_EX, RAR\_NMI - Return Address Registers

If a request for a mode change, for instance an interrupt request, is accepted when executing in a context *C*, the re-entry address of context *C* is automatically stored in the Return Address Register (RAR) associated with the interrupt context *I*. When the execution in the interrupt state *I* is finished and the *rets / rete* instruction is encountered, a change-of-flow to the address in the RAR associated with *I*, and the execution continues in the original context *C*.

#### RAR\_DBG - Return Address Register for Debug Mode

When Debug mode is entered, the Program Counter contents of the original mode is automatically saved in this register. When the debug routine is finished, the *retd* instruction copies the contents of RAR\_DBG into PC.

## JECR - Java Exception Cause Register

This register contains information needed for Java traps. See Java Technical Reference Manual for details.

#### JOSP - Java Operand Stack Pointer

This register holds the Java Operand Stack Pointer. See Java Technical Reference Manual for details. The register is initialized to 0 at reset.

# JAVA\_LVx - Java Local Variable Registers

The Java Extension Module uses these registers to temporarily store local variables. See Java Technical Reference Manual for details.

#### JTBA - Java Trap Base Address

This register contains the base address to the program code for the trapped Java instructions. See Java Technical Reference Manual for details.

#### JBCR - Java Write Barrier Control Register

This register is used by the garbage collector in the Java Virtual Machine. See Java Technical Reference Manual for details.

#### CONFIG0 / 1 - Configuration Register 0 / 1

Used to describe the processor, its configuration and capabilities. The contents and functionality of these registers is described in detail in Section 2.6 on page 16.

#### **COUNT - Cycle Counter Register**

The COUNT register increments once every clock cycle, regardless of pipeline stalls and flushes. The COUNT register can both be read and written. The count register can be used together with the COMPARE register to create a timer with interrupt functionality. The COUNT

register is written to zero upon reset. Incrementation of the COUNT register can not be disabled. The COUNT register will increment even though a compare interrupt is pending.

#### **COMPARE - Cycle Counter Compare Register**

The COMPARE register holds a value that the COUNT register is compared against. The COM-PARE register can both be read and written. When the COMPARE and COUNT registers match, a compare interrupt request is generated. This interrupt request is routed out to the interrupt controller, which may forward the request back to the processor as a normal interrupt request at a priority level determined by the interrupt controller. Writing a value to the COMPARE register clears any pending compare interrupt requests. The compare and exception generation feature is disabled if the COMPARE register contains the value zero. The COMPARE register is written to zero upon reset.

#### **TLBEHI - MMU TLB Entry Register High Part**

Used to interface the CPU to the TLB. The contents and functionality of the register is described in detail in Section 4. on page 48.

#### **TLBELO - MMU TLB Entry Register Low Part**

Used to interface the CPU to the TLB. The contents and functionality of the register is described in detail in Section 4. on page 48.

#### PTBR - MMU Page Table Base Register

Contains a pointer to the start of the Page Table. The contents and functionality of the register is described in detail in Section 4. on page 48.

#### **TLBEAR - MMU TLB Exception Address Register**

Contains the virtual address that caused the most recent MMU error. The contents and functionality of the register is described in detail in Section 4. on page 48.

#### **MMUCR - MMU Control Register**

Used to control the MMU and the TLB. The contents and functionality of the register is described in detail in Section 4. on page 48.

#### TLBARLO/HI - MMU TLB Accessed Register Low/High

Contains the Accessed bits for the TLB. The contents and functionality of the register is described in detail in Section 4. on page 48.

#### **PCCNT - Performance Clock Counter**

Clock cycle counter for performance counters. The contents and functionality of the register is described in detail in the AVR32 Architecture Manual.

#### PCNT0 / PCNT1 - Performance Counter 0 / 1

Counts the events specified by the Performance Counter Control Register. The contents and functionality of the register is described in detail in the AVR32 Architecture Manual.

#### PCCR - Performance Counter Control Register

Controls and configures the setup of the performance counters. The contents and functionality of the register is described in detail in the AVR32 Architecture Manual.

#### **BEAR - Bus Error Address Register**

**AVR32**

Physical address that caused a Data Bus Error. This register is Read Only. Writes are allowed, but are ignored.

# SABAL - Service Access Bus Address Low

Lower part of address to Service Access Bus used by debug system.

#### SABAH - Service Access Bus Address High

Higher part of address to Service Access Bus used by debug system.

# SABD - Service Access Bus Data

Data to or from Service Access Bus used by debug system.

# 2.6 Configuration Registers

Configuration registers are used to inform applications and operating systems about the setup and configuration of the processor on which it is running. Some of the fields in the configuration registers are fixed for all implementations using the AVR32 AP platform, while others, like the number of sets in each cache, can be different for each implementation of the platform. Such fields have IMPL in the Value field in the following tables. The programmer should refer to the data sheet for the specific product in order to obtain information on IMPL fields. The AVR32 implements the following read-only configuration registers.

# Figure 2-4. Configuration Registers.

CONFIG0

| 31           | 24 | 23 | 20 | 19 <sup>-</sup>      | 16 | 15 | 13 | 12 | 10 | 9 7  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------------|----|----|----|----------------------|----|----|----|----|----|------|---|---|---|---|---|---|---|

| Processor ID |    | -  |    | Processo<br>Revisior |    | A  | т  | A  | R  | MMUT | F | J | Р | 0 | s | D | R |

# CONFIG1

| 31 26   | 25 20   | 19 16 | 615 13 | 12 10 | 9 6  | 5 3  | 2 0  |

|---------|---------|-------|--------|-------|------|------|------|

| IMMU SZ | DMMU SZ | ISET  | ILSZ   | IASS  | DSET | DLSZ | DASS |

Table 2-4 shows the CONFIG0 fields.

| Table 2-4. CONFIG | G0 Fields |

|-------------------|-----------|

|-------------------|-----------|

| Name               | Bit   | Description                                                                                                              |                    |  |  |  |  |

|--------------------|-------|--------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|--|--|

| Processor ID       | 31:24 | Specifies the type of processor. This allows the application to distinguish between different processor implementations. |                    |  |  |  |  |

| RESERVED           | 23:20 | Reserved for future use.                                                                                                 |                    |  |  |  |  |

| Processor revision | 19:16 | Specifies the revision of the processor implementation.                                                                  |                    |  |  |  |  |

|                    |       | Architecture ty                                                                                                          | уре                |  |  |  |  |

| AT                 | 15:13 | Value                                                                                                                    | Semantic           |  |  |  |  |

|                    |       | 0                                                                                                                        | Unused in AVR32 AP |  |  |  |  |

|                    |       | 1                                                                                                                        | AVR32B             |  |  |  |  |

|                    |       | Other                                                                                                                    | Reserved           |  |  |  |  |

|                    |       | Architecture Revision                                                                                                    |                    |  |  |  |  |

|                    |       | Value                                                                                                                    | Semantic           |  |  |  |  |

| AR                 | 12:10 | 0                                                                                                                        | Unused in AVR32 AP |  |  |  |  |

|                    |       | 1                                                                                                                        | Revision 1         |  |  |  |  |

|                    |       | Other                                                                                                                    | Reserved           |  |  |  |  |

| Name | Bit | Description |                                           |  |  |

|------|-----|-------------|-------------------------------------------|--|--|

|      |     | MMU type    |                                           |  |  |

|      |     | Value       | Semantic                                  |  |  |

|      |     | 0           | Unused in AVR32 AP                        |  |  |

| MMUT | 9:7 | 1           | Unused in AVR32 AP                        |  |  |

|      |     | 2           | Shared TLB                                |  |  |

|      |     | 3           | Unused in AVR32 AP                        |  |  |

|      |     | Other       | Reserved                                  |  |  |

|      |     | Floating-po | pint unit implemented                     |  |  |

| F    |     | Value       | Semantic                                  |  |  |

|      | 6   | 0           | No FPU implemented                        |  |  |

|      |     | 1           | Unused in AVR32 AP                        |  |  |

|      |     | Java exten  | sion implemented                          |  |  |

| J    | _   | Value       | Semantic                                  |  |  |

|      | 5   | 0           | Unused in AVR32 AP                        |  |  |

|      |     | 1           | Java extension implemented                |  |  |

|      |     | Performan   | ce counters implemented                   |  |  |

|      |     | Value       | Semantic                                  |  |  |

| Р    | 4   | 0           | Unused in AVR32 AP                        |  |  |

|      |     | 1           | Performance Counters implemented          |  |  |

|      |     | On-Chip D   | ebug implemented                          |  |  |

| 0    | 0   | Value       | Semantic                                  |  |  |

| 0    | 3   | 0           | Unused in AVR32 AP                        |  |  |

|      |     | 1           | OCD implemented                           |  |  |

|      |     | SIMD instr  | uctions implemented                       |  |  |

| S    | 2   | Value       | Semantic                                  |  |  |

| 3    | 2   | 0           | Unused in AVR32 AP                        |  |  |

|      |     | 1           | SIMD instructions implemented             |  |  |

|      |     | DSP instru  | ictions implemented                       |  |  |

| D    | 1   | Value       | Semantic                                  |  |  |

|      |     | 0           | Unused in AVR32 AP                        |  |  |

|      |     | 1           | DSP instructions implemented              |  |  |

|      |     | Memory R    | ead-Modify-Write instructions implemented |  |  |

| R    | 0   | Value       | Semantic                                  |  |  |

|      | 0   | 0           | No RMW instructions implemented           |  |  |

|      |     | 1           | Unused in AVR32 AP                        |  |  |

Table 2-4.

CONFIG0 Fields (Continued)

Table 2-4 shows the CONFIG1 fields.

|  | Table 2-5. | CONFIG1 Fields |

|--|------------|----------------|

|--|------------|----------------|

| Name    | Bit   | Descriptio                                                                                                                                    | Description       |  |  |

|---------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|--|

| IMMU SZ | 31:26 | Not used in single-MMU systems like AVR32 AP.                                                                                                 |                   |  |  |

| DMMU SZ | 25:20 | Indicates the number of entries in the shared MMU in single-MMU systems like AVR32 AP. The number of entries in the MMU equals (DMMU SZ) + 1. |                   |  |  |

|         |       | Number of sets in ICACHE                                                                                                                      |                   |  |  |

|         |       | Value                                                                                                                                         | Semantic          |  |  |

|         |       | 0                                                                                                                                             | 1                 |  |  |

|         |       | 1                                                                                                                                             | 2                 |  |  |

|         |       | 2                                                                                                                                             | 4                 |  |  |

|         |       | 3                                                                                                                                             | 8                 |  |  |

|         |       | 4                                                                                                                                             | 16                |  |  |

|         |       | 5                                                                                                                                             | 32                |  |  |

|         | 10.10 | 6                                                                                                                                             | 64                |  |  |

| ISET    | 19:16 | 7                                                                                                                                             | 128               |  |  |

|         |       | 8                                                                                                                                             | 256               |  |  |

|         |       | 9                                                                                                                                             | 512               |  |  |

|         |       | 10                                                                                                                                            | 1024              |  |  |

|         |       | 11                                                                                                                                            | 2048              |  |  |

|         |       | 12                                                                                                                                            | 4096              |  |  |

|         |       | 13                                                                                                                                            | 8192              |  |  |

|         |       | 14                                                                                                                                            | 16384             |  |  |

|         |       | 15                                                                                                                                            | 32768             |  |  |

|         |       | Line size in ICACHE                                                                                                                           |                   |  |  |

|         |       | Value                                                                                                                                         | Semantic          |  |  |

|         |       | 0                                                                                                                                             | No ICACHE present |  |  |

| ILSZ    | 15:13 | 1                                                                                                                                             | 4 bytes           |  |  |

|         |       | 2                                                                                                                                             | 8 bytes           |  |  |

|         |       | 3                                                                                                                                             | 16 bytes          |  |  |

|         |       | 4                                                                                                                                             | 32 bytes          |  |  |

|         |       | 5                                                                                                                                             | 64 bytes          |  |  |

|         |       | 6                                                                                                                                             | 128 bytes         |  |  |

|         |       | 7                                                                                                                                             | 256 bytes         |  |  |

| Name | Bit   | Description              |               |  |

|------|-------|--------------------------|---------------|--|

|      | 12:10 | Associativity of ICACHE  |               |  |

| IASS |       | Value                    | Semantic      |  |

|      |       | 0                        | Direct mapped |  |

|      |       | 1                        | 2-way         |  |

|      |       | 2                        | 4-way         |  |

|      |       | 3                        | 8-way         |  |

|      |       | 4                        | 16-way        |  |

|      |       | 5                        | 32-way        |  |

|      |       | 6                        | 64-way        |  |

|      |       | 7                        | 128-way       |  |

|      |       | Number of sets in DCACHE |               |  |

|      |       | Value                    | Semantic      |  |

|      |       | 0                        | 1             |  |

|      |       | 1                        | 2             |  |

|      |       | 2                        | 4             |  |

|      |       | 3                        | 8             |  |

|      |       | 4                        | 16            |  |

|      | 9:6   | 5                        | 32            |  |

| DSET |       | 6                        | 64            |  |

| DSEI | 9.0   | 7                        | 128           |  |

|      |       | 8                        | 256           |  |

|      |       | 9                        | 512           |  |

|      |       | 10                       | 1024          |  |

|      |       | 11                       | 2048          |  |

|      |       | 12                       | 4096          |  |

|      |       | 13                       | 8192          |  |

|      |       | 14                       | 16384         |  |

|      |       | 15                       | 32768         |  |

**Table 2-5.**CONFIG1 Fields (Continued)

| Name | Bit | Descriptio              | Description       |  |  |

|------|-----|-------------------------|-------------------|--|--|

|      |     | Line size in DCACHE     |                   |  |  |

|      |     | Value                   | Semantic          |  |  |

|      |     | 0                       | No DCACHE present |  |  |

|      |     | 1                       | 4 bytes           |  |  |

| DLSZ | 5:3 | 2                       | 8 bytes           |  |  |

| DLSZ | 5.3 | 3                       | 16 bytes          |  |  |

|      |     | 4                       | 32 bytes          |  |  |

|      |     | 5                       | 64 bytes          |  |  |

|      |     | 6                       | 128 bytes         |  |  |

|      |     | 7                       | 256 bytes         |  |  |

|      |     | Associativity of DCACHE |                   |  |  |

|      |     | Value                   | Semantic          |  |  |

|      |     | 0                       | Direct mapped     |  |  |

|      |     | 1                       | 2-way             |  |  |

| DASS | 2:0 | 2                       | 4-way             |  |  |

|      | 2:0 | 3                       | 8-way             |  |  |

|      |     | 4                       | 16-way            |  |  |

|      |     | 5                       | 32-way            |  |  |

|      |     | 6                       | 64-way            |  |  |

|      |     | 7                       | 128-way           |  |  |

#### Table 2-5. CONFIG1 Fields (Continued)

# 3. Pipeline

# 3.1 Overview

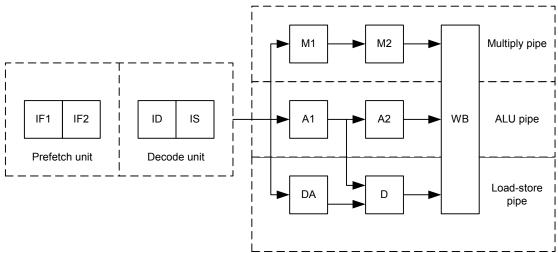

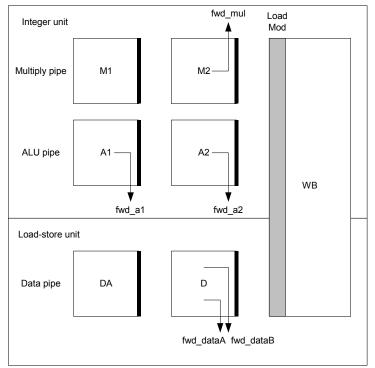

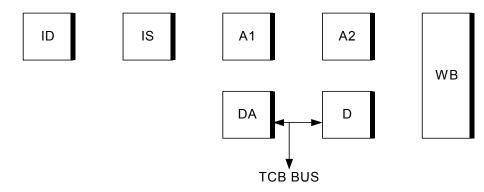

AVR32 AP is a pipelined processor with seven pipeline stages. The pipeline has three subpipes, namely the Multiply pipe, the Execute pipe and the Data pipe. These pipelines may execute different instructions in parallel. Instructions are issued in order, but may complete out of order (OOO) since the subpipes may be stalled individually, and certain operations may use a subpipe for several clock cycles.

The following figure shows an overview of the AVR32 AP pipeline stages.

Figure 3-1. The AVR32 AP pipeline stages.

The following abbreviations are used in the figure:

- IF1, IF2 Instruction Fetch 1 and 2

- ID Instruction Decode

- IS Instruction Issue

- A1, A2 ALU stage 1 and 2

- M1, M2 Multiply stage 1 and 2

- DA Data Address calculation stage

- D Data cache access

- WB Writeback

# 3.2 Prefetch unit

The prefetch unit comprises the IF1 and IF2 pipestages, and is responsible for feeding instructions to the decode unit. The prefetch unit fetches 32 bits at a time from the instruction cache and places them in a FIFO prefetch buffer. At the same time, one instruction, either RISC extended or compact, or Java, is fed to the decode stage.

The instruction fetches are probed for the presence of change-of-flow instructions. If such instructions are found, the prefetch unit will try to determine the destination of the instruction and continue fetching instructions from there. The branch penalty will be eliminated if the prefetch unit correctly predicts the destination of a change-of-flow instruction. When possible, the

prefetch unit will remove the change-of-flow instruction from the pipeline and replace it with the target instruction. This is called branch folding.

In Java mode, the prefetch unit is able to recognize certain Java instruction pairs and merge them together to one merged instruction. These merged instructions are passed on to ID as one instruction.

Details about the prefetch unit is given in chapter 5.

# 3.3 Decode unit

The decode unit generates the necessary signals in order for the instruction to execute correctly. The ID stage accepts one instruction each clock cycle from the prefetch unit. This instruction is then decoded, and control signals and register file addresses are generated. If the instruction cannot be decoded, an illegal instruction or unimplemented instruction exception is issued. The ID stage also contains a state machine required for controlling multicycle instructions.

The ID stage performs the remapping of register file addresses from logical to physical addresses. This is used both for remapping register address into the different contexts, and for remapping registers to the Java operand stack if the R bit in the status register is set. The ID stage also contains the Java Operand Stack Pointer (JOSP) register which is used to address the Java operand stack if the CPU is running in Java mode.

The IS stage performs register file reads and keeps track of data hazards in the pipeline. If hazards exist, pipelines are frozen as needed in order to resolve the hazard.

# 3.4 ALU pipeline

The ALU pipeline performs most of the data manipulation instructions, like arithmetical and logical operations. The A1 stage performs the following tasks:

- Target address calculation and condition check for change-of-flow instructions. The A1 pipestage checks if the branch prediction performed by the prefetch unit was correct. If not, the prefetch unit is notified so that the pipeline can be flushed, the correct instruction can be fetched and the BTB can be updated.

- Condition code checking for conditional instructions.

- Address calculation for indexed memory accesses

- Writeback address calculation for the LS pipeline.

- All flag setting for arithmetical and logical instructions.

- The A2 stage performs the following tasks:

- The saturation needed by satadd and satsub.

- The operation and flag setting needed by satrnds, satrndu, sats and satu.

# 3.5 Multiply pipeline

All multiply instructions execute in the multiply pipeline. This pipeline contains a 32 by 16 multiplier array, and 16x16 and 32x16 multiplications therefore have an issue latency of one cycle. Multiplication of 32 by 32 bits require two iterations through the multiplier array, and therefore needs several cycles to complete. Additional cycles may be needed if an accumulation is to be performed. This will stall the multiply pipeline until the instruction is complete.

A special accumulator cache is implemented in the MUL pipeline. This cache saves the multiplyaccumulate result in dedicated registers in the MUL pipeline, as well as writing them back to the register file. This allows subsequent MAC instructions to read the accumulator value from the cache, instead of from the register file. This will speed up MAC operations by one clock cycle. If a MAC instruction targets a register not found in the cache, one clock cycle is added to the MAC operation, loading the accumulator value from the register file into the cache. In the next cycle, the MAC operation is restarted automatically by hardware. If a multiply (not MAC) instruction is executed with target address equal to that of a valid cached register, the multiply instruction will update the cache. All multiply and divide instructions will update the cache with its result, so that a subsequent MAC to the same register will not have to preload the cache.

The accumulator cache can hold one doubleword accumulator value, or one word accumulator value. Hardware ensures that the accumulator cache is kept consistent. If another pipeline updates one of the registers kept in the accumulator cache, the cache is invalidated. The cache is automatically invalidated after reset.

Some of the multiply instructions, *machh.d*, *macwh.d*, *mulwh.d* and *mulnwh.d*, produce a 48-bit result that is to be placed in two registers. These instructions all have an issue latency of 1, even though the MUL pipe only has one writeback port and two results are produced. This is handled by delaying the writeback of the low register until the MUL pipeline is idle. Then, the low register can be written back without stalling the MUL pipe. The high register is written back to the register file when the instruction leaves the M2 stage. This scheme allows several of these instructions to be issued consecutively, with no stalls due to writeback port congestion. This will increase performance in MUL-intensive applications such as DSP algorithms. The MUL pipe can only hold one delayed register for writeback, so a MUL instruction writing to another register will have to stall one cycle in IS if a writeback is pending in the MUL pipe. Hazard detection is performed on the pending writeback register, so any instruction reading a register pending writeback will stall in IS until the value is forwardable in M2.

The multiply pipeline also contains a divider, performing multicycle 32-by-32 signed and unsigned division with both quotient and remainder outputs.

In general, the MUL instructions do not set any flags. However, some of the MUL instructions may set the saturate (Q) flag. No hazard detection is performed on this setting of the Q flag. The programmer must ensure that such a Q flag update has propagated to the status register before using the Q flag.

# 3.6 Load-store pipeline

The load-store (LS) pipeline is able to read or write up to two registers per clock cycle, if the data is 64-bit aligned. The address is calculated by the A1 pipe stage for indexed and load-extracted-index accesses, the DA stage performs all other address calculations. Thereafter the address is passed on to the LS pipe and output to the cache, together with the data to write if the access is a write. If the access is a read, the read data is returned from the cache in the D stage. If the read data requires typecasting or other manipulation like performed by *Idins* or *Idswp*, this manipulation is performed in the WB stage.

The LS pipeline also contains hardware for performing load and store multiple instructions decoupled from the rest of the core. For such instructions, the A1 stage calculates the pointer writeback address if needed. The load or store is then decoupled from the integer unit, and the integer unit may execute sequential instructions if no hazards occur. Load and store of multiple registers are performed by accessing 2 words at a time. If the first address is not 64-bit aligned, the first access is performed as a single word. The rest of the transfer is then performed as 64 bit accesses. The last transfer may need to be performed as a 32 bit access, depending on the number of registers to load or store.

For code efficiency purposes, the programmer should always try to rearrange the instructions in the code in such a way that no data stalls will occur.

## 3.6.1 Support for unaligned addresses

The LS pipeline is able to perform certain word-sized load and store instructions of any alignment, and word-aligned *st.d* and *ld.d*. Any other unaligned memory access will cause an MMU address exception. All coprocessor memory access instructions require word-aligned pointers. Doubleword-sized accesses with word-aligned pointers will automatically be performed as two word-sized accesses.

The following table shows the instructions with support for unaligned addresses. All other instructions require aligned addresses. Accessing an unaligned address may require several clock cycles, refer to Section 10. on page 154 for details.

| Instruction                               | Supported alignment |

|-------------------------------------------|---------------------|

| ld.w                                      | Any                 |

| st.w                                      | Any                 |

| lddsp                                     | Any                 |

| lddpc                                     | Any                 |

| stdsp                                     | Any                 |

| ld.d                                      | Word                |

| st.d                                      | Word                |

| All coprocessor memory access instruction | Word                |

Table 3-1.

Instructions with unalignment support

AVR32

# 3.7 Writeback

The three subpipes share a writeback (WB) stage with three register file write ports. If the three subpipes produces four results at the same time, the MUL pipeline is temporarily stalled until a writeback port is available. The WB stage also contains logic for:

- Sign- or zero-extention of data loaded from cache.

- Execution of Idins and Idswp.

- Output formatting of data loaded from unaligned addresses.

# 3.8 Forwarding hardware and hazard detection

The pipeline is implemented in such a way that the programmer in most cases will not have to consider hazards between instructions when writing code. Efficient operand forwarding mechanisms are implemented in order to minimize pipeline stalls due to data dependencies. When dependencies exist, the hardware will stall the affected parts of the pipeline in order to guarantee correct execution. Data forwarding is done automatically and is invisible to the user. This ensures that all code will execute correctly, even though the pipeline may have to be stalled in some cases. The user should be aware of these stalls and try to rewrite the code so that no such dependencies arise. This will result in faster execution.

Since instructions are allowed to complete out of order, both Write-After-Read (WAR), Write-After-Write (WAW) and Read-After-Write (RAW) hazards may occur. If an instruction is affected by a hazard, or will provoke a hazard, it is frozen in the IS stage until the hazard is resolved. This will also freeze all upstream pipeline stages. All downstream stages are allowed to continue execution. Instructions storing data to memory will read the data to store from the register file in the D pipeline stage. This pipeline stage has a dedicated hazard detection and forwarding unit. If the data to store to memory is not available in the D stage, the LS pipe will have to stall. Newer instructions may still start executing in the other pipelines.

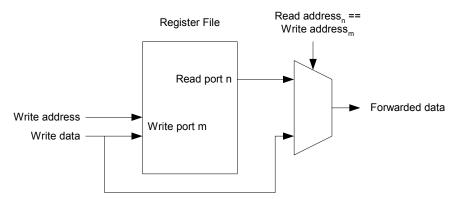

#### 3.8.1 IS stage forwarding

The IS stage is able to forward data from the register file inputs to the register file outputs. If data to write is present at the write ports of the register file at the same time as the register is read, the data not yet written will be read. This ensures that data from the writeback stages are forwarded to the register file outputs. This is illustrated in Figure 3-2:

**Figure 3-2.** Forwarding inside the IS stage

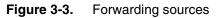

#### 3.8.2 Forwarding sources

All operations that produce valid results are forwarded. All data are forwarded directly from the inputs of pipeline registers. The following figure shows the forwarding sources, and the name of the forwarded signals. Each of the forwarded signals carry a word-sized value. Pipeline registers are illustrated as a thick black line, the load modification unit is illustrated as a gray box.

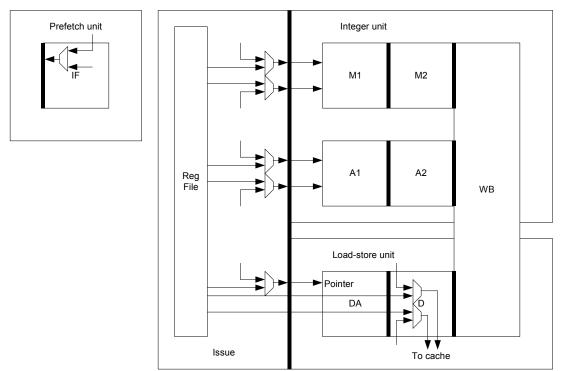

# 3.8.3 Forwarding destinations

The forwarded data is input to the IS stage. The IS stage has logic deciding whether the value read from the register file is valid, or if a forwarded value should be used. This is illustrated in Figure 3-4. Forwarded data is shown with bent arrows, and data from the previous pipeline stage is shown in straight arrows. The forwarded value really consists of all the possible forward values described in Figure 3-3, but is shown as a single value for simplicity. The prefetch unit also receives forwarded data. This data is used for calculating an instruction fetch address for change-of-flow instructions. Target addresses for change-of-flow instructions are produced either by the A1 stage, or the WB stage.

Figure 3-4. Forwarding destinations

# 3.9 Hazards not handled by the hardware

All hazards occurring between normal arithmetical, logical, load-store and change-of-flow instructions are handled automatically by hardware. There are, however, a few instruction sequences which must be sequenced by the user. These sequences are described in this chapter. The programmer can assume that any instruction sequence other than the sequences explicitly mentioned in this chapter will work without any special consideration.

# 3.9.1 Accessing system registers with mtsr and mfsr

The *mtsr* instruction writes the contents of a register into a system register. The system registers control the behaviour of the CPU. The programmer must make sure that any *mtsr* instruction has committed and has altered the state of the system in the desired way before issuing any new instructions that depend on this new state. This can be done by inserting *nop* instructions, or other instructions that do not depend on the new state generated by the *mtsr* instruction.

Table 2-2, "System Registers implemented in AVR32 AP," on page 10 details the timing for writes into the different system registers. The system registers are written as the *mtsr* instruction leaves the pipeline stage described in the table. The system registers are read as the *mfsr* instruction leaves the pipeline stage described in the table. As soon as a system register is read by *mfsr*, it can be forwarded as any regular register file register.

Some of the system registers are located inside modules on the TCB bus. These are written when the *mtsr* instruction leaves the D pipeline stage. Instructions depending on a *mtsr* to these system registers being committed must therefore wait in the IS stage until the effects of the *mtsr* is guaranteed to be visible to the instruction. The following code demonstrates a write to the ASID field of TLBEHI, followed by a *rete* to an address which requires the new ASID to be visible. A *nop* is inserted to guarantee that the *mtsr* leaves the D stage at the same time as *rete* leaves the A1 stage. In the following cycle, the icache will start fetching at the specified address

and observe the newly updated ASID. Register r0 is assumed to contain the correct value to write into TLBEHI.

```

mtsr TLBEHI, r0

nop

rete

```

#### 3.9.2 Writing to the status register with ssrf and csrf

These instructions have the same timing as a *mtsr* to the system register.

#### 3.9.3 Writing to and using the JOSP register

The JOSP register is used to determine which register file register to access when in Java mode. This is needed because the 8 elements on top of the Java operand stack are located in the register file. Since the register addresses are generated in the ID stage, JOSP is located here.

JOSP is automatically updated to the correct value when executing Java bytecodes in Java mode. One may also need to update the JOSP register manually, either with the *incjosp* instruction, or using *mtsr/mfsr* for reading/writing JOSP.

When updating JOSP with *incjosp*, JOSP is updated with the new value when *incjosp* has left ID. The *incjosp* instruction reads the value of JOSP when it is in ID, and writes the new value as it leaves ID. If the *incjosp* instruction is flushed from the pipe before being committed for some reason like an interrupt or a taken change-of-flow instruction, hardware automatically restores the correct value to the JOSP register. The JOSP register will be restored to the value it had after the last completed instruction.

When updating JOSP with *mtsr*, JOSP is updated with the new value when *mtsr* has left A1. The user is responsible for not letting any instruction that uses JOSP leave ID before mtsr has written the new JOSP value. This may require inserting *nop* instructions between *mtsr* and any instruction using JOSP.

The following assembly code illustrates coding to avoid hazards when accessing JOSP. Two *nop* instructions are inserted to make sure that the new value of JOSP written by *mtsr* as *mtsr* leaves A1 is visible to the *incjosp* instruction when it enters ID. A *mfsr* instruction may follow immediately after *incjosp*, as *incjosp* writes the new JOSP value when it leaves ID, while *mfsr* reads JOSP while it is in A1.

```

mtsr JOSP, r0

nop

incjosp -2

mfsr r1, JOSP

```

The following assembly code is another illustration of coding to avoid hazards when accessing JOSP. The two sets of code perform identical operations. This code sets the R bit in the status register in order to enable remapping of the register file to a Java operand stack. This effectively remaps r0 to r7 into a Java operand stack, where the mapping from logical register to physical register is dependent on the value of JOSP. Note that the second code example is strongly discouraged to use in practice, since no JOSP over/underflow detection is performed. The code is presented only to show the differences in timing between the two ways of writing to JOSP.

In the first code, *incjosp* changes the value of JOSP when it is in ID. The new value of JOSP is therefore visible when the *add* instruction enters ID.

**AVR32**

In the second code, *mtsr* writes the new value of JOSP as it leaves A1. As the *add* instruction needs JOSP to be updated when it enters ID because of the register remapping, two *nop* instructions must be inserted.

```

ssrf R

incjosp -2

add r0, r0

ssrf R

mfsr r8, JOSP

sub r8, 2

mtsr JOSP, r8

nop

nop

add r0, r0

```

## 3.9.4 Execution of TLB instructions

The TLB instructions *tlbr, tlbw* and *tlbs* are used to maintain the data in the TLB. They use the TCB bus to access the MMU, and the instruction is dispatched to the MMU when the instruction is in the D pipeline stage. The programmer must make sure that any writes to the TLB with the *tlbw* instructions are completed before the TLB entry is used in an icache or dcache memory access. This is handled automatically for any dcache memory access, since any load/store instructions flow through the same pipeline as the *tlbw* instruction, and the *tlbw* instruction will have left the D stage before any load/store instruction enters it. Any icache access that is to use the page table entry written by *tlbw* must wait until the *tlbw* instruction, as illustrated in the code below, which shows a part of a ITLB miss handler. The *rete* instruction wishes to use the page table entry written by *tlbw* to generate the physical address of the instruction to return to.

tlbw nop rete

#### 3.9.5 Execution of cache instructions

The *cache* instruction perform various cache-relatated operations, like invalidation of lines. Some of these operations are harmless, and need no sequencing or hazard consideration. Other operations, like invalidation, require more concern. The programmer must make sure that any invalidation is committed before any instruction the depends on the invalidation already being performed is allowed to execute.

The *cache* instruction use the TCB bus to access the caches, and the instruction is dispatched to the caches when the instruction is in the D pipeline stage. The programmer must make sure that any *cache* instructions are completed before any icache or dcache memory access that depends on the cache instruction is executed. This is handled automatically for any dcache memory access, since any load/store instructions flow through the same pipeline as the *cache* instruction, and the *cache* instruction will have left the D stage before any load/store instruction enters it. Any icache access that is dependent on the *cache* instruction must wait until the *cache* instruction is in the D pipeline stage. This may require inserting a *nop* or another unrelated instruction, as illustrated in the code below. The *rjmp* instruction wishes to jump to a location

labeled flushedaddress that must be flushed from the cache. INVALIDATEI is a macro that is defined to be the command for invalidation of the icache.

cache INVALIDATEI nop rjmp flushedaddress

#### 3.9.6 Hazards on the Q flag

Some of the instructions in the instruction set updates the status register Q flag. Many of these instructions, like satadd, generate the new Q flag after a single cycle so no hazards are present between these instructions and other instructions. The *sats, satu, satrnds, satrndu* and some multiply instructions, require several cycles before updating the Q flag. The required Q flag latency for each of these instructions is listed in Section 10. on page 154. The user must make sure that any of these instructions have completed and updated the Q flag before using the Q flag in any computations. In the following example, a *satrnds* instruction is followed by a branch-if-q-set instruction. A *nop* is needed in order to guarantee correct execution.

satrnds r0>>0, 5

nop

brgs targetaddress

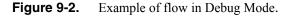

## 3.10 Event handling

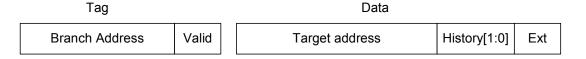

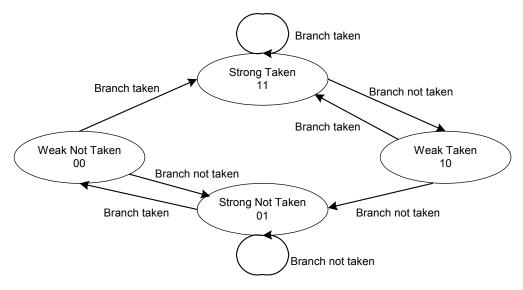

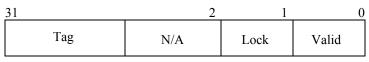

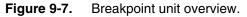

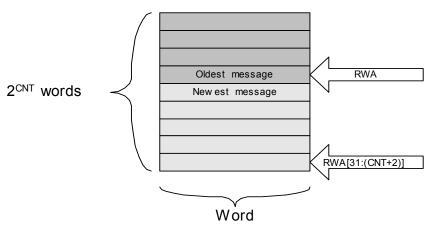

The CPU is able to respond to different events. An event can be either an interrupt or an exception. Interrupts are requests from external modules and are routed through the interrupt controller. Exceptions are system events that require handling outside normal program flow.